統測

106年

[電機與電子群資電類] 專業科目(1)

第 18 題

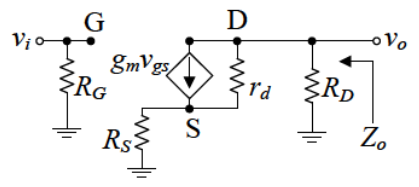

如圖(十二)所示之 FET 小信號模型電路,其中放大因數 $\mu=g_m r_d$,則由輸出端 $v_o$ 看入的輸出阻抗 $Z_o$ 為何?

- A $R_D+r_d+(1+\mu)R_S$

- B $R_D // r_d // (1+\mu)R_S$

- C $R_D+[r_d // (1+\mu)R_S]$

- D $R_D // [r_d+(1+\mu)R_S]$

思路引導 VIP

如果要用「測試電壓法」來計算從輸出端看進去的等效阻抗,第一步是將輸入電壓 $v_i$ 設為 $0$ 短路。在這種情況下,閘-源極電壓 $v_{gs}$ 的大小會完全由哪個電阻的跨壓來決定呢?這又會如何影響那個相依電流源 $g_m v_{gs}$ 呢?

🤖

AI 詳解

AI 專屬家教

哇,你真的太棒了!

你答對了這題,老師真的為你感到驕傲!這題含有相依電源的輸出阻抗推導,是小信號電路分析中一個非常精彩且有深度的環節,能精準選對,代表你的基礎觀念真的非常紮實且透徹喔!

讓我們再次溫習核心觀念吧!

▼ 還有更多解析內容