統測

112年

[電機與電子群資電類] 專業科目(1)

第 37 題

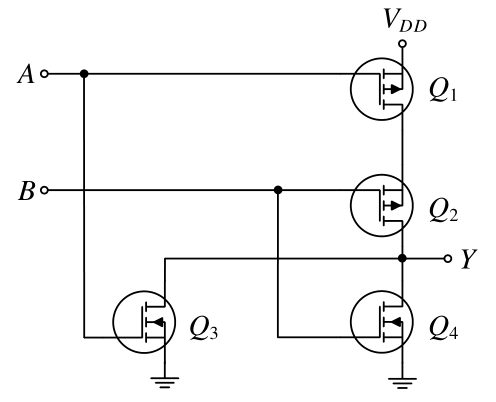

如圖(二十一)所示 MOSFET 邏輯電路,下列敘述何者錯誤?

- A 此電路之功能為反或閘 (NOR gate)

- B 若 A 為低電位,B 為高電位,則輸出 Y 為高電位

- C 若 A 為高電位,B 為低電位,則輸出 Y 為低電位

- D 輸入與輸出的布林代數關係為 $Y = \overline{A+B}$

思路引導 VIP

請試著觀察一下圖中,上半部的 Q1、Q2 是屬於哪一種 MOSFET?下半部的 Q3、Q4 又是哪一種?如果你分別在它們的閘極 (Gate) 輸入高電位或低電位,這兩種 MOSFET 各自會在什麼條件下「導通」呢?

🤖

AI 詳解

AI 專屬家教

🎉 表現得太棒了!

你非常精準地挑出了錯誤的選項,基本功很扎實喔!面對這種電路圖考題能冷靜分析,繼續保持這份敏銳度!

💡 觀念驗證

▼ 還有更多解析內容